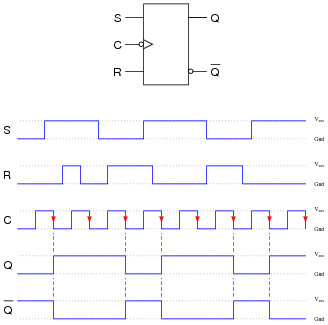

They are supposed to be compliments of each other. This is an invalid state because the values of both Q and Q’ are 0.

If both the values of S and R are switched to 0, then the circuit remembers the value of S and R in their previous state. In both the states you can see that the outputs are just compliments of each other and that the value of Q follows the value of S. You can figure out and contribute to our open source project on our git hub repo.Fig.1 SR Flip-flop Using NOR gates Operationįrom the diagram it is evident that the flip flop has mainly four states. Open-source project: Open source is very very important for us that's why we are contributing to open-source development as well. Real-time chat: We have an extensive amount of geeks behind the scene they are helping you to solve every problem you are facing real-time Voice APIs:- Every question and answers have voice APIs by pressing the listen to this question button user will be able to listen to the content which helps students from different background.Īlgorithm driven video delivery: Every video from our database is delivered against the content which students are browsing with the help of our proprietary algorithm.Įduladder career: We have a robust ATS developed on the top of famous open source ATS called open cats the APIs which we have built on the top of the same will deliver the best and suitable job to the visitor who is browsing in our platform. Question and answers:- Where every question is asked and answered by community and the best question and answers are voted up so the visitors will get the best answers. Show how a D flip flop converted into JK flipflop?ĭesign a mode 5 counter using T flip flop Write a short note on clocked RS Flip - Flop. Give the difference between Latch and Flip Flop. Replication capabilities in MySQL based on the propagation of SQL statements from master to slave is called _ ?MySQL

Which of the following flip-flop is used as latch? After three clock cycles the output state P, Q is (respectively),GATE CSE 2000 The following arrangement of master-slave flip flops has the initial state of P, Q as 0, 1 (respectively).

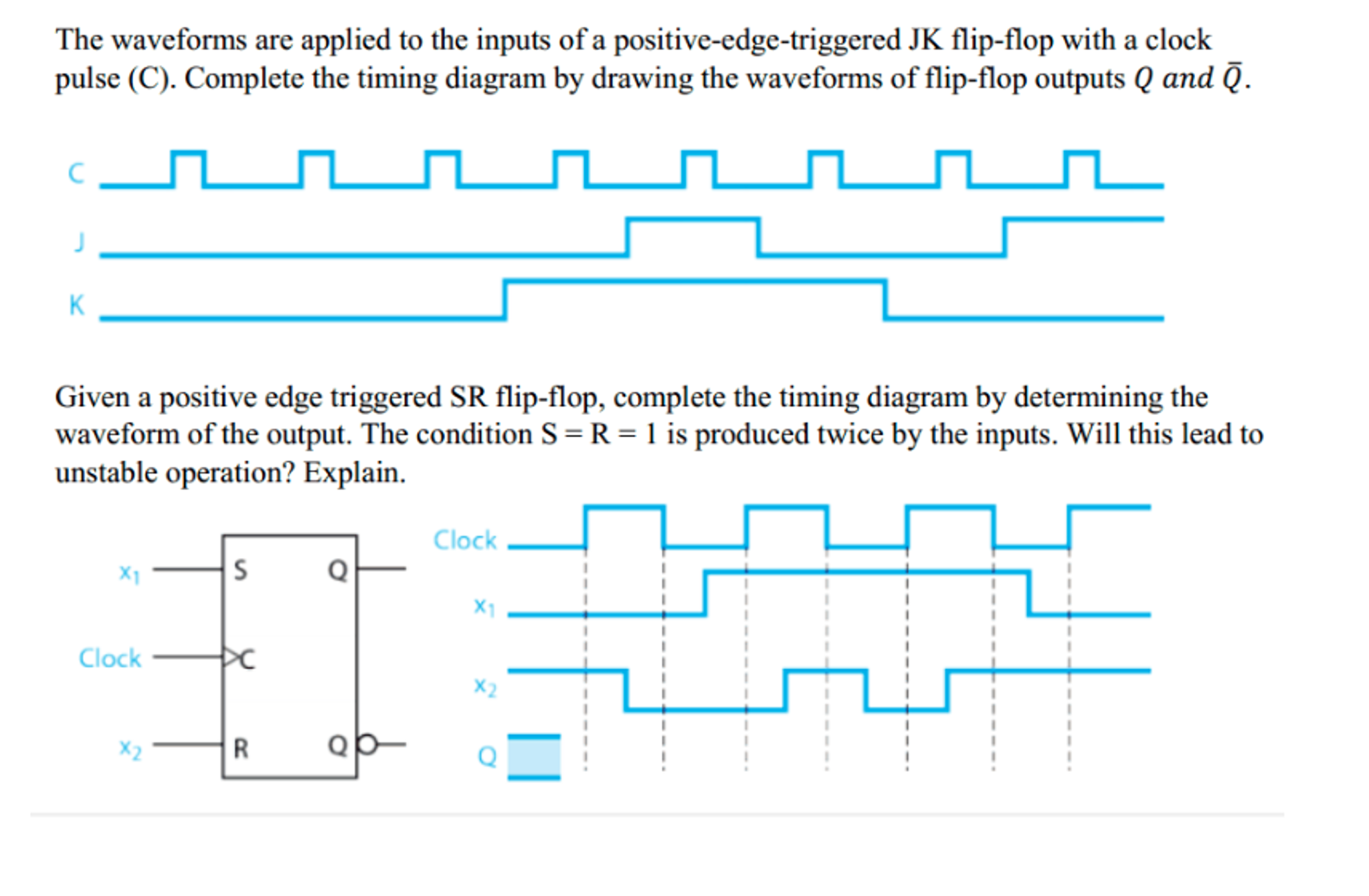

What is the major advantage of the J-K flip-flop over the S-R flip-flop? CBSE-english-2016Ĭan the automatic RC circuit be used to set a flip-flop rather than reset the flip-flop? explain. Write a short story with the help of outline below. What is the difference between level and edge triggering? Explain the working of master slave J - K flip flop? With the help of a neat diagram explain the working of a Master Slave JK flip flopĪ positive edge-triggered D flip-flop is connected to a positive edge-triggered JK flipflop as follows. With the help of block diagram explain the working of a JK Master Slave flip flop? Explain how a master slave J K Flip Flop works?

0 kommentar(er)

0 kommentar(er)